## Feedback Linearization of RF Power Amplifiers

Joel L. Dawson Thomas H. Lee

# Feedback Linearization of RF Power Amplifiers

This page intentionally left blank

## FEEDBACK LINEARIZATION OF RF POWER AMPLIFIERS

JOEL L. DAWSON Stanford University

THOMAS H. LEE Stanford University eBook ISBN: 1-4020-8062-X Print ISBN: 1-4020-8061-1

©2004 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2004 Kluwer Academic Publishers Boston

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: and Kluwer's eBookstore at: http://kluweronline.com http://ebooks.kluweronline.com

To Mari

This page intentionally left blank

## Contents

| De              | edicati | ion     |                                      | v    |

|-----------------|---------|---------|--------------------------------------|------|

| Li              | st of F | Figures |                                      | xi   |

| Li              | st of T | Tables  |                                      | XV   |

| Acknowledgments |         |         |                                      | xvii |

| 1.              | INT     | RODUC   | CTION                                | 1    |

|                 | 1.1     | Motiva  | ation                                | 1    |

|                 | 1.2     | Organ   | ization                              | 2    |

| 2.              | OPT     | TMAL    | ALLOCATION OF LOCAL FEEDBACK IN      |      |

|                 | MU      | LTISTA  | GE AMPLIFIERS                        | 5    |

|                 | 2.1     | Ampli   | fier stage models                    | 6    |

|                 |         | 2.1.1   | Linearized static model              | 6    |

|                 |         | 2.1.2   | Static nonlinear model               | 6    |

|                 |         | 2.1.3   | Linearized dynamic model             | 8    |

|                 |         | 2.1.4   | Static noise model                   | 8    |

|                 | 2.2     | Ampli   | fier analysis                        | 8    |

|                 |         | 2.2.1   | Gain and output swing                | 9    |

|                 |         | 2.2.2   | Sensitivity                          | 10   |

|                 |         | 2.2.3   | Nonlinearity                         | 10   |

|                 |         | 2.2.4   | Bandwidth                            | 11   |

|                 |         | 2.2.5   | Delay and rise-time                  | 12   |

|                 |         | 2.2.6   | Noise and dynamic range              | 12   |

|                 |         | 2.2.7   | SFDR and IIP linearity measures      | 13   |

|                 | 2.3     | Geom    | etric programming                    | 14   |

|                 |         | 2.3.1   | Geometric programming in convex form | 14   |

|                 |         | 2.3.2   | Solving geometric programs           | 15   |

|                 | 2.4     | Optim   | al local feedback allocation         | 16   |

|    |     | 2.4.1   | Closed-loop gain                                        | 16 |

|----|-----|---------|---------------------------------------------------------|----|

|    |     | 2.4.2   | Maximum signal swing                                    | 16 |

|    |     | 2.4.3   | Sensitivity                                             | 17 |

|    |     | 2.4.4   | Bandwidth                                               | 17 |

|    |     | 2.4.5   | Noise and dynamic range                                 | 18 |

|    |     | 2.4.6   | Delay and rise-time                                     | 18 |

|    |     | 2.4.7   | Third-order distortion                                  | 18 |

|    |     | 2.4.8   | SFDR and IIP3                                           | 18 |

|    | 2.5 | Design  | Examples                                                | 18 |

|    |     | 2.5.1   | Trade-offs among bandwidth, gain, and noise             | 19 |

|    |     | 2.5.2   | SFDR versus gain                                        | 24 |

|    |     | 2.5.3   | Stage selection                                         | 25 |

|    | 2.6 | Geome   | tric programming summary                                | 26 |

|    | 2.7 | An exa  | mple application                                        | 27 |

|    |     | 2.7.1   | Linearized static model                                 | 28 |

|    |     | 2.7.2   | Static nonlinear model                                  | 28 |

|    |     | 2.7.3   | Linearized dynamic model                                | 29 |

|    |     | 2.7.3.1 | An alternative formulation: open-circuit time constants | 30 |

|    |     | 2.7.4   | Static noise model                                      | 31 |

|    | 2.8 | Local f | eedback allocation for power amplifier linearization    | 32 |

| 3. | THE | PROBL   | LEM OF LINEARIZATION                                    | 33 |

|    | 3.1 | The tra | deoff between linearity and power efficiency            | 33 |

|    | 3.2 | Can no  | nlinear system theory help?                             | 35 |

|    | 3.3 | An ove  | rview of linearization techniques                       | 35 |

|    |     | 3.3.1   | Power backoff                                           | 35 |

|    |     | 3.3.2   | Predistortion                                           | 36 |

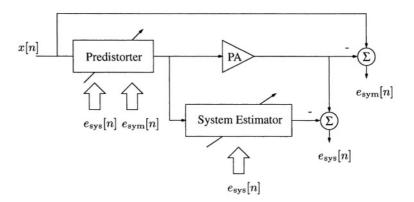

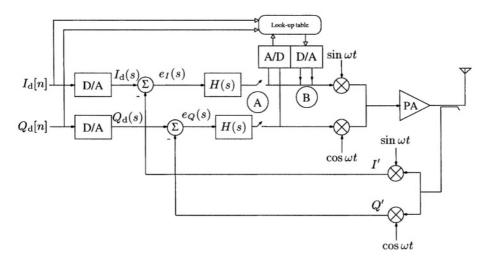

|    |     | 3.3.3   | Adaptive predistortion                                  | 37 |

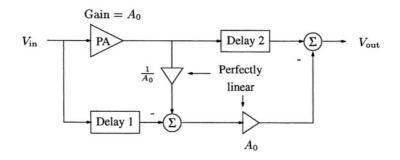

|    |     | 3.3.4   | Feedforward                                             | 38 |

|    |     | 3.3.5   | Dynamic biasing                                         | 39 |

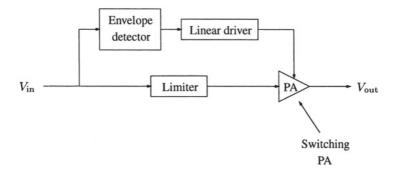

|    |     | 3.3.6   | Envelope elimination and restoration                    | 39 |

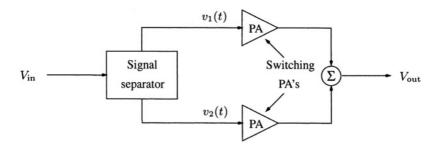

|    |     | 3.3.7   | LINC                                                    | 40 |

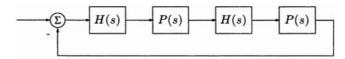

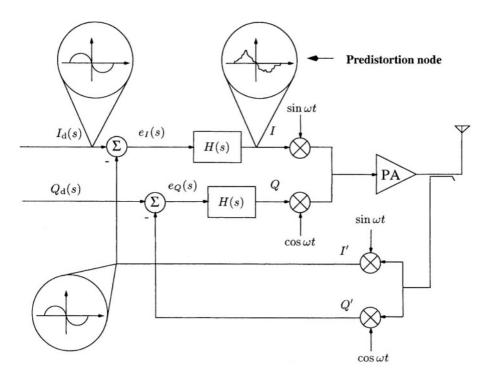

|    |     | 3.3.8   | Cartesian feedback                                      | 41 |

| 4. | PHA | SE ALI  | GNMENT IN CARTESIAN FEEDBACK SYSTEMS                    | 43 |

|    | 4.1 | -       | uences of phase misalignment in Cartesian feedback      |    |

|    |     | system  |                                                         | 43 |

|    |     | 4.1.1   | Terminology Convention                                  | 44 |

|    |     | 4.1.2   | Impact of phase misalignment on stability               | 44 |

|    |     | 4.1.3 Compensation for robustness to phase misalignment | 46  |

|----|-----|---------------------------------------------------------|-----|

|    | 4.2 | A nonlinear regulator for maintaining phase alignment   | 48  |

|    |     | 4.2.1 Nonlinear dynamical system                        | 48  |

|    |     | 4.2.2 Stability concerns                                | 50  |

|    |     | 4.2.3 Quadrature error in the mixers                    | 51  |

|    |     | 4.2.4 Impact of multiplier offsets                      | 51  |

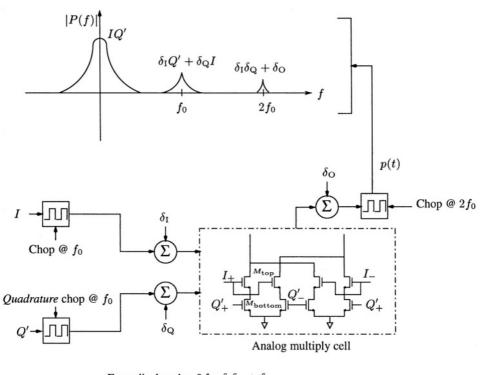

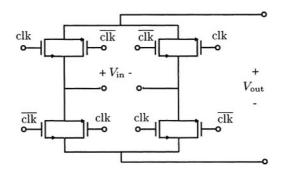

|    | 4.3 | A new technique for offset-free analog multiplication   | 52  |

|    |     | 4.3.1 Limits on performance                             | 55  |

|    | 4.4 | Summary                                                 | 56  |

| 5. | A F | ULLY INTEGRATED CARTESIAN FEEDBACK SYSTEM               | 57  |

|    | 5.1 | Motivation for pursuing Cartesian feedback              | 57  |

|    | 5.2 | Motivation for a monolithic implementation              | 60  |

|    | 5.3 | CFB IC at the system level                              | 61  |

|    | 5.4 | The phase alignment system                              | 62  |

|    |     | 5.4.1 Circuit details                                   | 66  |

|    |     | 5.4.1.1 Basic multiplier cell                           | 66  |

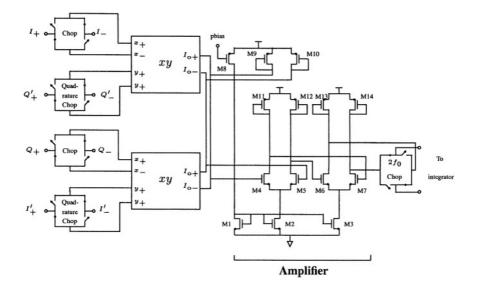

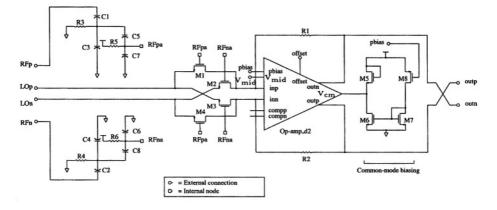

|    |     | 5.4.1.2 Phase error computation                         | 70  |

|    |     | 5.4.1.3 An analog integrator                            | 71  |

|    |     | 5.4.1.4 A constant 1-norm controller                    | 78  |

|    |     | 5.4.1.5 Forming the matrix rotation operator            | 82  |

|    |     | 5.4.2 Phase alignment system results                    | 84  |

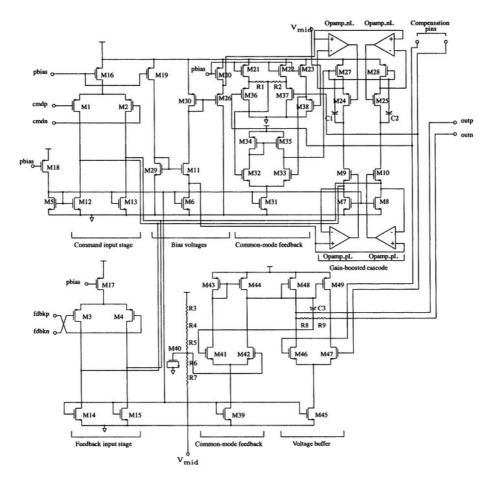

|    | 5.5 | The linearization circuitry                             | 88  |

|    |     | 5.5.1 Circuit details                                   | 88  |

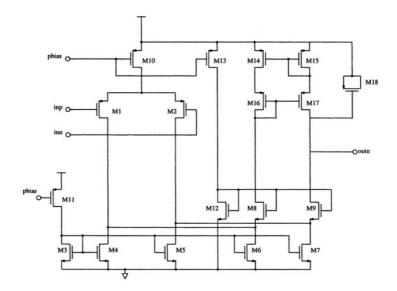

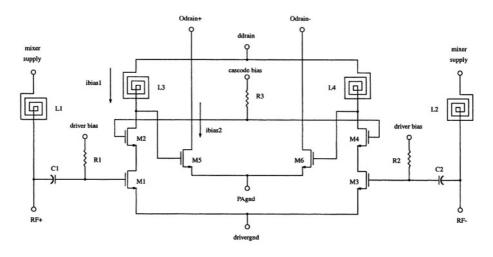

|    |     | 5.5.1.1 Loop driver                                     | 89  |

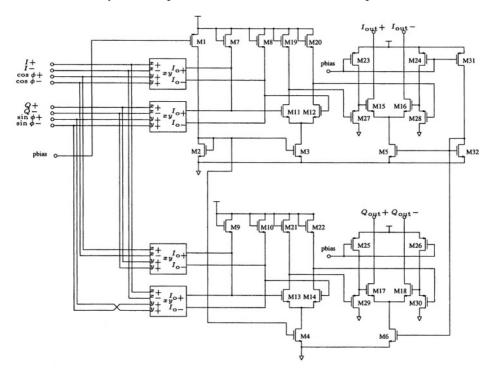

|    |     | 5.5.1.2 Analog matrix rotation                          | 92  |

|    |     | 5.5.1.3 Upconversion mixer                              | 93  |

|    |     | 5.5.1.4 Power amplifier                                 | 93  |

|    |     | 5.5.1.5 Downconverter                                   | 95  |

|    |     | 5.5.1.6 Polyphase filters                               | 99  |

|    |     | 5.5.1.7 Constant-gm biasing                             | 100 |

|    |     | 5.5.2 Linearization system results                      | 102 |

|    |     | 5.5.2.1 Linearization behavior                          | 102 |

|    |     | 5.5.2.2 Loop stability                                  | 104 |

|    | 5.6 | Summary                                                 | 105 |

| 6.    | CON         | ICLUSION                                       | 113 |

|-------|-------------|------------------------------------------------|-----|

|       | 6.1         | Summary                                        | 113 |

|       | 6.2         | Future work                                    | 114 |

| Ap    | pendi       | ices                                           | 117 |

| А     | The         | First Prototype of the Phase Alignment Concept | 117 |

|       | A.1         | Phase shifter                                  | 117 |

|       | A.2         | Phase error and integrator                     | 118 |

|       | A.3         | Test results                                   | 118 |

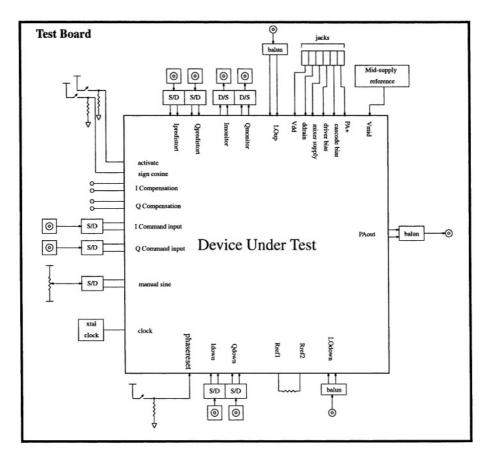

| В     | The         | Experimental Setup for CFB IC                  | 123 |

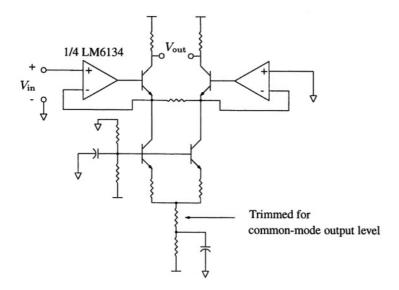

|       | <b>B</b> .1 | Single-ended-to-differential conversion        | 123 |

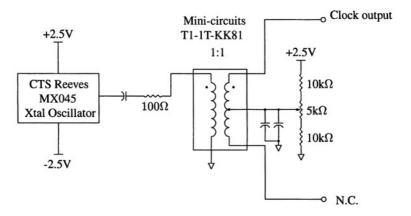

|       | B.2         | Clock reference                                | 123 |

|       | B.3         | Overview of test board                         | 124 |

| Re    | feren       | ces                                            | 127 |

| Index |             |                                                | 133 |

## **List of Figures**

| 2.1  | Block diagram of multistage amplifier.                                                                                                               | 5  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2  | Linearized static model of amplifier stage.                                                                                                          | 7  |

| 2.3  | Nonlinear static model of amplifier stage.                                                                                                           | 7  |

| 2.4  | Linear dynamic model of amplifier stage.                                                                                                             | 8  |

| 2.5  | Static noise model of amplifier stage.                                                                                                               | 9  |

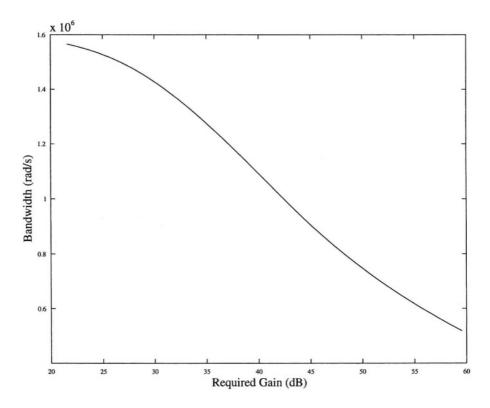

| 2.6  | Maximum bandwidth versus limit on input-referred noise.                                                                                              | 20 |

| 2.7  | Optimal feedback allocation pattern, for maximum band-<br>width with limit on input-referred noise. Gain = 23.5dB.                                   | 21 |

| 2.8  | Maximum bandwidth versus required closed-loop gain.<br>Maximum input-referred noise = 4.15e-7 V rms.                                                 | 22 |

| 2.9  | Optimal feedback allocation pattern for maximum band-<br>width versus required closed-loop gain. Maximum input-<br>referred noise = $4.15e-7$ V rms. | 23 |

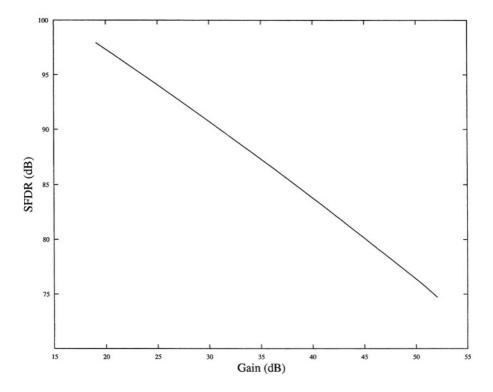

| 2.10 | Maximum spurious-free dynamic range versus required gain.                                                                                            | 24 |

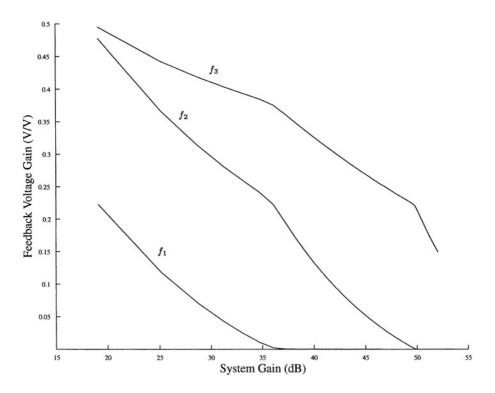

| 2.11 | Optimal feedback allocation pattern for maximum spurious-<br>free dynamic range versus required gain.                                                | 25 |

| 2.12 | CMOS source-coupled pair and differential half-circuit.                                                                                              | 27 |

| 2.13 | Source degeneration as a form of feedback.                                                                                                           | 28 |

| 2.14 | Modification for nonlinear static model.                                                                                                             | 29 |

| 2.15 | Modeling dynamics using the Miller approximation.                                                                                                    | 29 |

| 2.16 | MOSFET noise model.                                                                                                                                  | 31 |

| 2.17 | MOSFET gate and drain noise.                                                                                                                         | 31 |

| 3.1  | A high-efficiency power amplifier.                                                                                                                   | 34 |

| 3.2  | Using predistortion to linearize a power amplifier.                                                                                                  | 37 |

| 3.3  | An example of adaptive predistortion.                                                                                                                | 37 |

| 3.4  | Feedforward linearization.                                                                                                                                            | 38 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.5  | Envelope elimination and restoration.                                                                                                                                 | 39 |

| 3.6  | The LINC concept.                                                                                                                                                     | 40 |

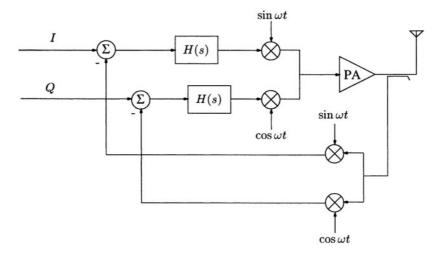

| 3.7  | Cartesian feedback.                                                                                                                                                   | 41 |

| 4.1  | Typical Cartesian feedback system.                                                                                                                                    | 44 |

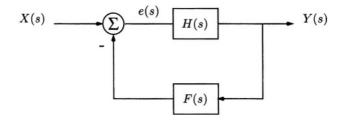

| 4.2  | Simple feedback system.                                                                                                                                               | 44 |

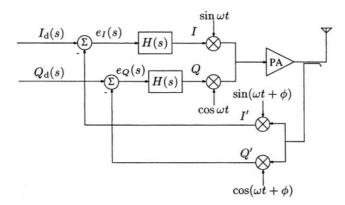

| 4.3  | Cartesian feedback under 90-degree misalignment.                                                                                                                      | 46 |

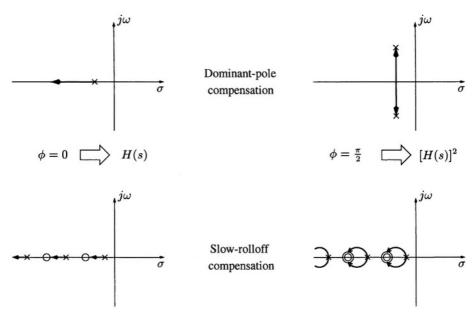

| 4.4  | Root locus plots for dominant-pole and slow-rolloff $(\frac{k}{\sqrt{s}})$ compensation.                                                                              | 47 |

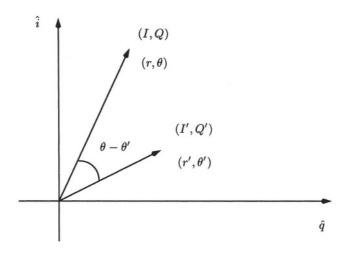

| 4.5  | Rotation of the baseband symbol due to phase misalignment.                                                                                                            | 49 |

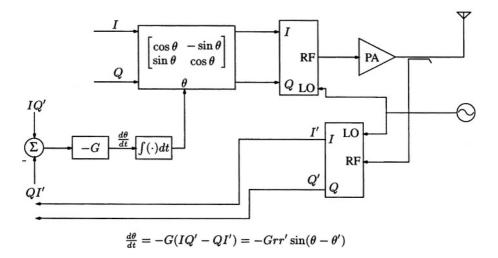

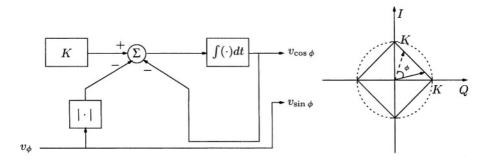

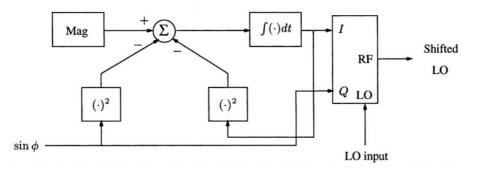

| 4.6  | Phase alignment concept.                                                                                                                                              | 50 |

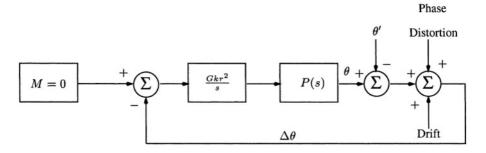

| 4.7  | Linearized phase regulation system. 'M' is the desired misalignment, which is nominally zero.                                                                         | 51 |

| 4.8  | New technique for offset-free analog multiplication.                                                                                                                  | 53 |

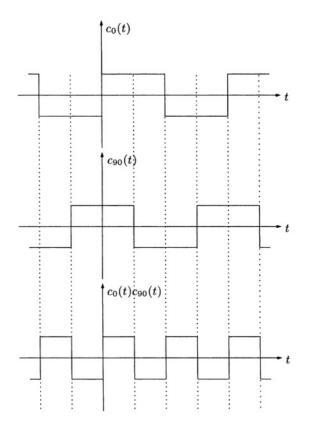

| 4.9  | Graphically computing $c_0(t)c_{90}(t)$ .                                                                                                                             | 55 |

| 5.1  | The predistorting action of Cartesian feedback.                                                                                                                       | 58 |

| 5.2  | Cartesian feedback used to train a predistorter.                                                                                                                      | 59 |

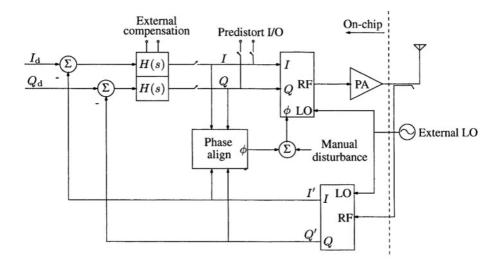

| 5.3  | Conceptual diagram of CFB IC.                                                                                                                                         | 62 |

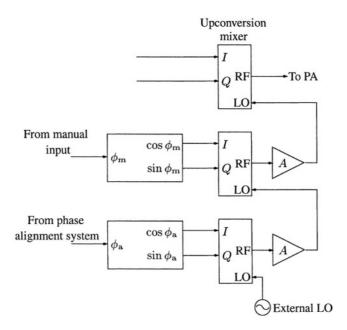

| 5.4  | Phase alignment by phase shifting the local oscillator.                                                                                                               | 63 |

| 5.5  | Phase alignment by rotating the baseband symbol.                                                                                                                      | 64 |

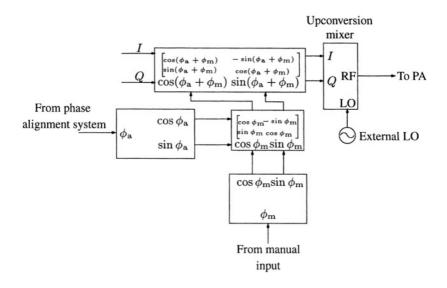

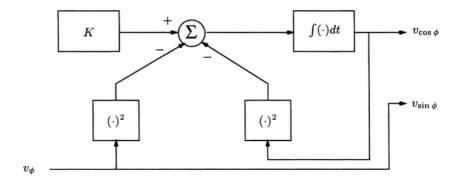

| 5.6  | Analog technique for generating $v_{\sin\phi}$ and $v_{\cos\phi}$ .                                                                                                   | 65 |

| 5.7  | Analog rotation using the 1-norm.                                                                                                                                     | 65 |

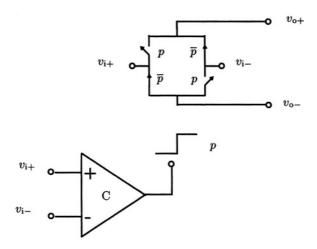

| 5.8  | Using CMOS voltage switches and a comparator to re-<br>alize a folding amplifier. Switches are closed when their<br>respective control signal is high.                | 66 |

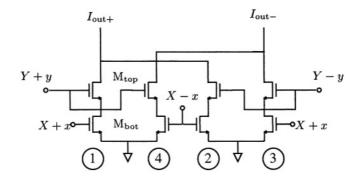

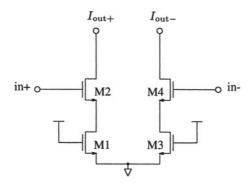

| 5.9  | Basic topology for multiplier cell. All transistors connected to a $y$ input are sized $M_{top}$ , and all transistors connected to a $x$ input are sized $M_{bot}$ . | 67 |

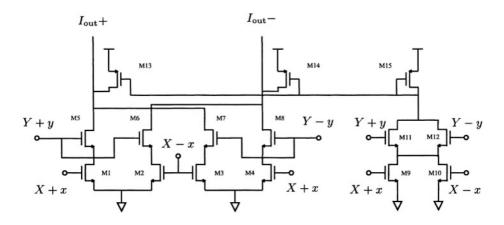

| 5.10 | Multiplier cell.                                                                                                                                                      | 69 |

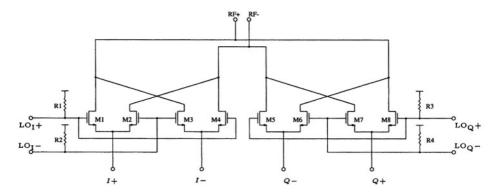

| 5.11 | Commutating mixer for chopping. NMOS devices are sized 3/0.24, PMOS 9/0.24.                                                                                           | 70 |

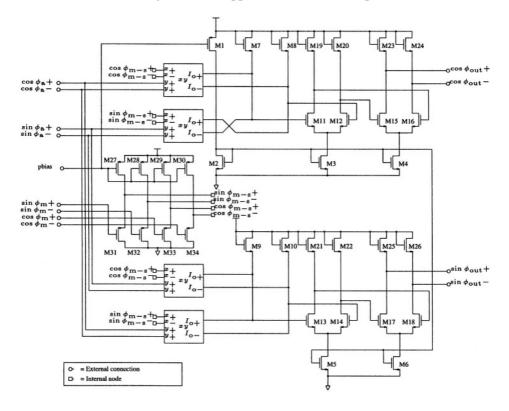

| 5.12 | Phase error computation.                                                                                                                                              | 71 |

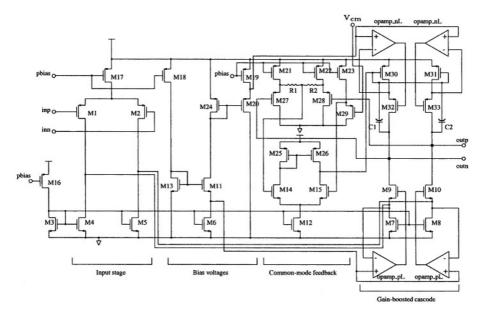

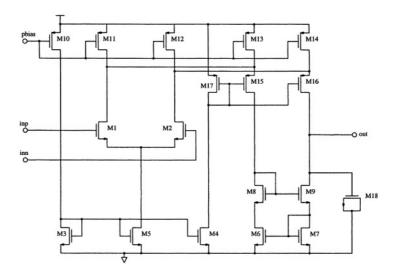

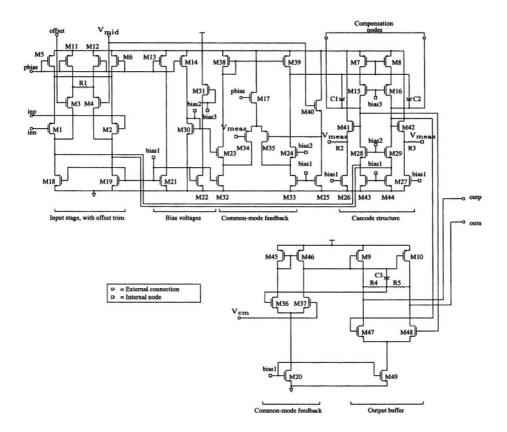

| 5.13 | Op-amp_d1, a fully differential op-amp for the S.C. integrator.                                                                                                       | 72 |

| 5.14 | Opamp_pL, a single-ended op-amp for low common-<br>mode inputs.                                                                                                       | 74 |

| 5.15 | Opamp_nL, a single-ended op-amp for high common-<br>mode inputs.                                                                                                      | 74 |

| 5.16 | Switched-capacitor, non-inverting integrator for phase<br>alignment system. Switches are complementary: NMOS |           |

|------|--------------------------------------------------------------------------------------------------------------|-----------|

| - 1- | 2/0.24 , PMOS 6/0.24 .                                                                                       | 75        |

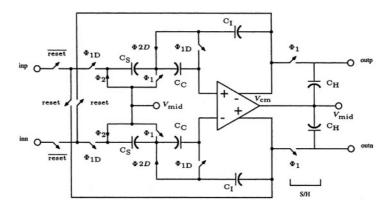

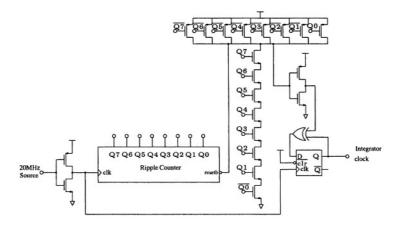

| 5.17 | Chopping clocks derived from off-chip source.                                                                | 77        |

| 5.18 | Integrator clock, which transitions on the trailing edge                                                     | 70        |

| 5 10 | of the external 20MHz source.                                                                                | 78<br>79  |

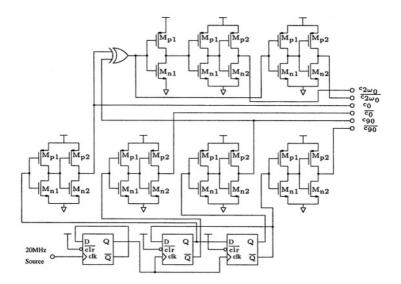

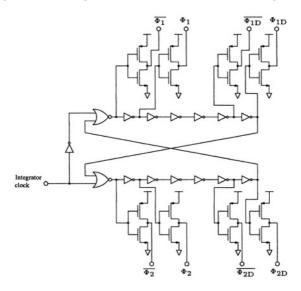

| 5.19 | Circuit for generating clock phases.                                                                         | 78<br>70  |

| 5.20 | Constant 1-norm controller: circuit realization of figure 5.7.                                               | 79        |

| 5.21 | Differential transconductor.                                                                                 | 80        |

| 5.22 | Folding amplifier for constant 1-norm controller.                                                            | 81        |

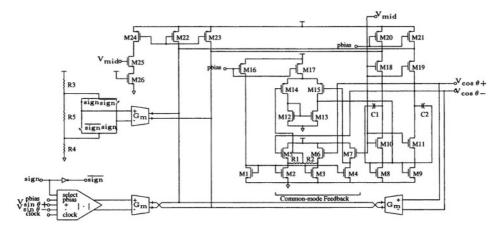

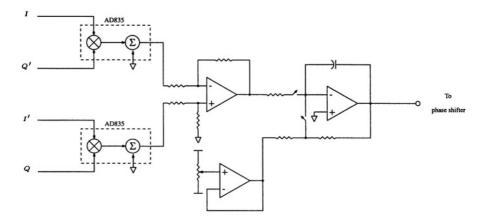

| 5.23 | Computation of the rotation operator.                                                                        | 83        |

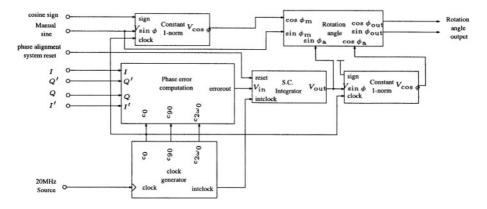

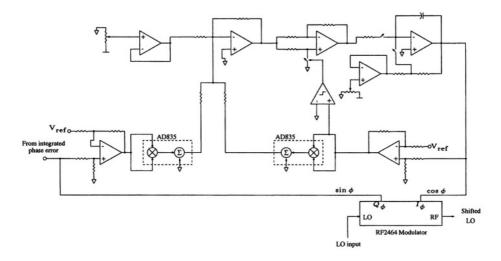

| 5.24 | Overview diagram of phase alignment system.                                                                  | 84        |

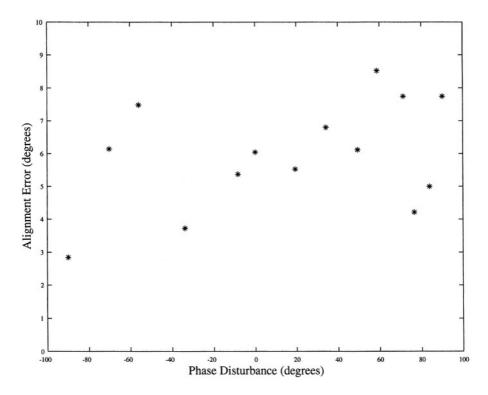

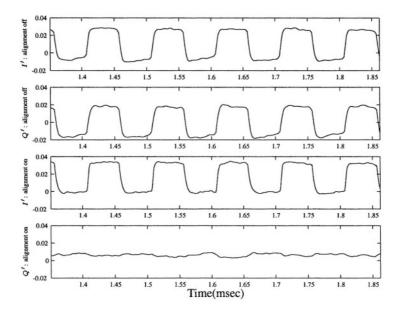

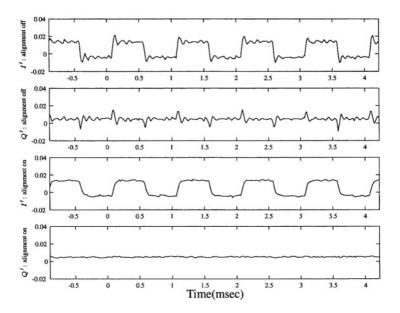

| 5.25 | Phase alignment performance for a 500mV amplitude, 10 kHz square wave.                                       | 85        |

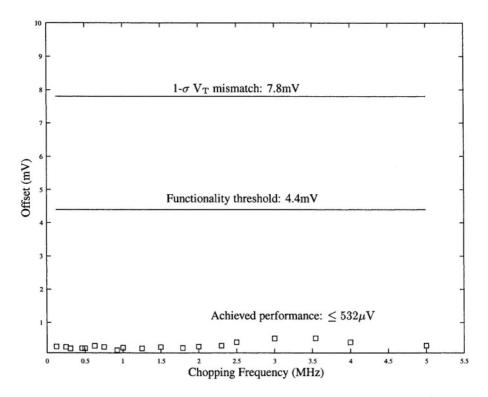

| 5.26 | Effective output offset, $\delta_0$ , of the chopper-stabilized multipliers of figure 5.12.                  | 87        |

| 5.27 | Trace capture of a phase alignment experiment. The Cartesian feedback loop is open.                          | 88        |

| 5.28 | Illustration of phase alignment stabilizing the closed-                                                      |           |

|      | loop CFB system.                                                                                             | 89        |

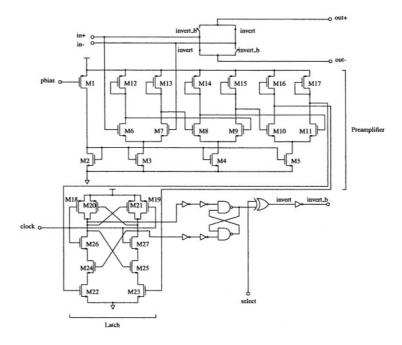

| 5.29 | Loop driver amplifier.                                                                                       | 90        |

| 5.30 | Baseband_g <sub>m</sub> , a circuit to carry out the matrix rotation.                                        | 92        |

| 5.31 | Upconversion mixer. All transistors are sized $2 \times 50.4/0.24$ , all resistors are $10k\Omega$ .         | 94        |

| 5.32 | Power amplifier.                                                                                             | 94        |

| 5.33 | Potentiometric downconversion mixer, together with bi-                                                       |           |

|      | asing and capacitive RF attenuator.                                                                          | 96        |

| 5.34 | Op-amp_d2, a fully differential op-amp for the down-                                                         | 00        |

| 5.25 | conversion mixer.                                                                                            | 98<br>00  |

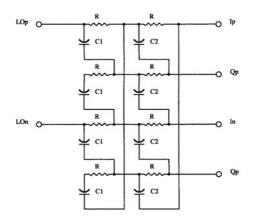

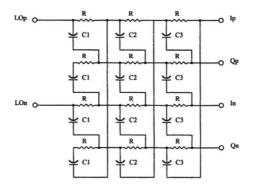

| 5.35 | A two-stage polyphase filter.                                                                                | 99<br>100 |

| 5.36 | A three-stage polyphase filter.                                                                              | 100       |

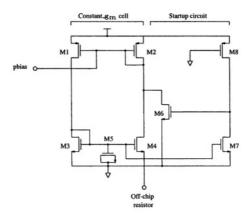

| 5.37 | $Constant_{gm}$ cell, which establishes the voltage 'pbias' for the entire chip.                             | 101       |

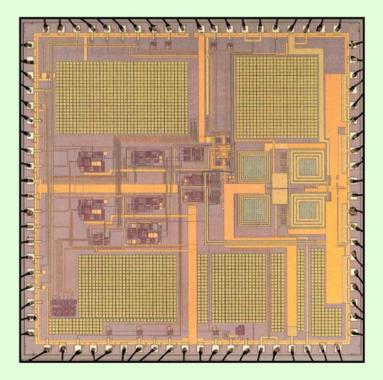

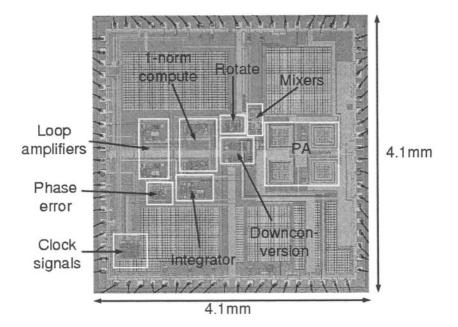

| 5.38 | Die photo.                                                                                                   | 107       |

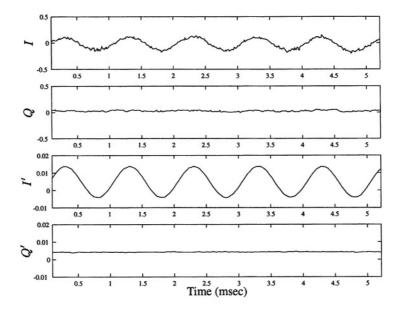

| 5.39 | Comparison between predistortion inputs and down-<br>converter outputs for no misalignment.                  | 108       |

| 5.40 | Comparison between predistortion inputs and down-<br>converter outputs for 45-degree misalignment.           | 108       |

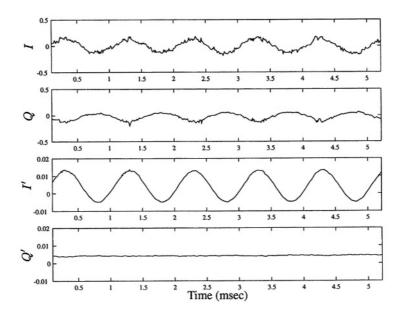

| 5.41 | Frequency-domain example of linearization behavior.                                                             | 109 |

|------|-----------------------------------------------------------------------------------------------------------------|-----|

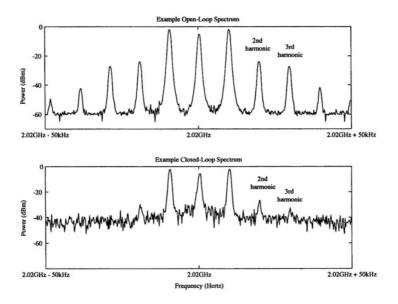

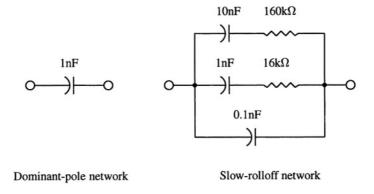

| 5.42 | Compensation networks used in stability experiments.                                                            | 109 |

| 5.43 | Step response of aligned, dominant-pole compensated system.                                                     | 110 |

| 5.44 | Step response of aligned, uncompensated system.                                                                 | 110 |

| 5.45 | Step response of aligned, slow-rolloff compensated system.                                                      | 111 |

| 5.46 | Step response comparison between dominant-pole and slow-rolloff compensated systems for 90-degree misalignment. | 111 |

| A.1  | Phase shifter.                                                                                                  | 117 |

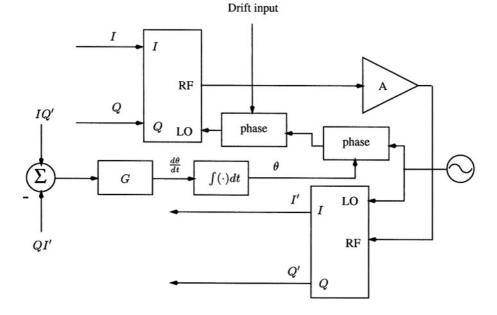

| A.2  | Phase shifter implementation.                                                                                   | 118 |

| A.3  | Phase error computation and integration.                                                                        | 119 |

| A.4  | Test setup.                                                                                                     | 119 |

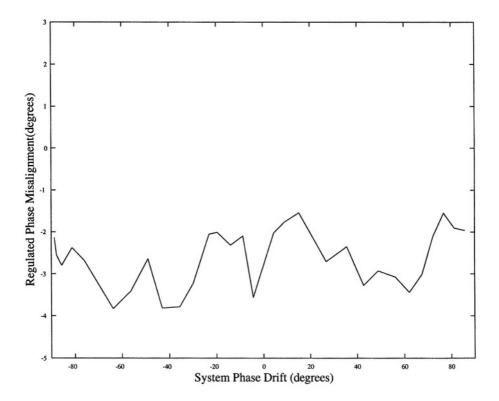

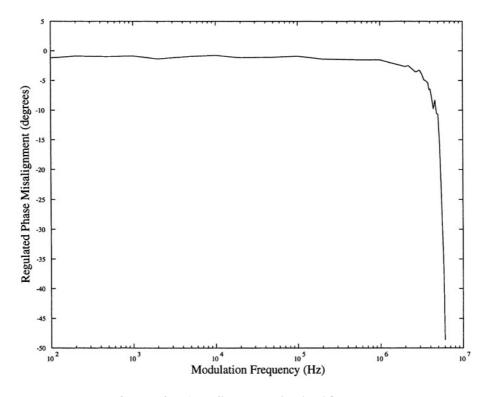

| A.5  | Measured phase alignment vs. system drift                                                                       | 120 |

| A.6  | Phase alignment vs. baseband frequency                                                                          | 121 |

| B.1  | Converting from single-ended to differential signals.                                                           | 124 |

| B.2  | The on-board clock reference.                                                                                   | 124 |

| B.3  | The test board.                                                                                                 | 125 |

## **List of Tables**

| 2.1  | Candidate stages.                                                                                       | 26  |

|------|---------------------------------------------------------------------------------------------------------|-----|

| 5.1  | Multiplier elements.                                                                                    | 69  |

| 5.2  | Phase error computation elements. Quiescent current includes current draw of multiplier cells.          | 70  |

| 5.3  | Elements for integrator op-amp. Quiescent current in-<br>cludes current draw of Opamp_nL and Opamp_pL.  | 72  |

| 5.4  | Opamp_pL elements.                                                                                      | 73  |

| 5.5  | Opamp_nL elements.                                                                                      | 75  |

| 5.6  | Integrator capacitor values.                                                                            | 75  |

| 5.7  | Elements for chopping clocks.                                                                           | 77  |

| 5.8  | Constant 1-norm elements. Quiescent current includes current draw of folding amplifier and $G_m$ cells. | 79  |

| 5.9  | Differential transconductor elements.                                                                   | 80  |

| 5.10 | Folding amplifier elements.                                                                             | 82  |

| 5.11 | Rotation operator elements.                                                                             | 84  |

| 5.12 | Elements for loop driver amplifier. Quiescent current                                                   |     |

|      | includes current draw of Opamp_nL and Opamp_pL.                                                         | 91  |

| 5.13 | Matrix rotation operator elements.                                                                      | 93  |

| 5.14 | Power amplifier elements.                                                                               | 95  |

| 5.15 | Downconversion mixer elements. Quiescent current in-<br>cludes current draw of Op-amp_d2.               | 96  |

| 5.16 | Elements for downconversion op-amp.                                                                     | 98  |

| 5.17 | Polyphase filter elements.                                                                              | 100 |

| 5.18 | Constant-gm bias cell elements.                                                                         | 101 |

| A.1  | Comparison with examples from the literature.                                                           | 120 |

|      |                                                                                                         |     |

This page intentionally left blank

#### Acknowledgments

It is with great pleasure that we acknowledge the many people who have supported the work described in this book. In particular, Professor Stephen Boyd deserves credit for originally proposing the investigation of Chapter 2, and for working closely with us to bring it to fruition. Professors Bruce Wooley and Donald Cox graciously read a draft of this entire manuscript, and provided valuable and insightful comments.

We would also like to thank a number of institutions for their support of this investigation. Lucent Technologies, the National Science Foundation, and the Hertz Foundation all provided fellowship support, as did Stanford University through its Stanford Graduate Fellows program. National Semiconductor continues to provide Stanford students with free use of its  $0.25\mu$ m CMOS process, an almost unbelievable luxury for students in our field. Agilent Technologies supported this work through the FMA program at CIS. This was largely due to the efforts of Dr. Jim Hollenhorst and Paul Corredoura, who in addition provided friendship and were sources of stimulating technical discussion.

Stanford's Center for Integrated Systems was a wonderful place to work, and this was due in large part to the presence of its graduate students. Dr. Dawson gladly acknowledges all members, past and present, of the Lee (SMIrC), Wooley, and Wong groups who have given their friendship and collaboration. Dr. David Su, formerly of the Wooley group, was particularly generous with his advice and insight during the hardware testing stages of this investigation.

Ann Guerra, the administrative assistant to Professors Lee and Wooley, has been a marvel at making administrative tasks run smoothly. She does this with a warmth, kindness, and humor that have greatly eased the passage of many students through the Ph.D. program. We take this opportunity to thank her for being a wonderful person to work with.

Dr. Dawson would also like to acknowledge his family, which was a source of unending love and support. They showed him that he is not, and never has been, alone in his endeavors. Finally, Marisol Negrón deserves a special acknowledgment for her steadfast love and support during the toughest days of this investigation. It is only fitting that this book be dedicated to her.

#### Chapter 1

### **INTRODUCTION**

Research activity in the area of radio-frequency (RF) circuit design has surged in the last decade in direct response to the enormous market demand for inexpensive, portable, high data rate wireless transceivers. Our expectations for such transceivers, such as cellular phones, rise as they become seemingly ubiquitous. Once, the simple fact of a fairly reliable wireless voice connection was sufficient and even exciting. Now, crystal-clear voice with no lapses in coverage is actively sought, together with the capability to act as a web portal and even a digital assistant. All of this must be accomplished by a device that is cheap enough to be virtually given away, small enough to justify the claim of portability, and frugal enough with power demands to last a long time on a single battery charge.

Cellular phones are just one example of a market that has spurred recent research activity. Wireless local-area networks (WLAN's) are another relatively new application of RF circuit techniques, as is the popular Global Positioning System (GPS). Meeting this demand for a kind of general connectivity involves a host of fascinating technical challenges. Among these, many are associated with the power amplifier, the system block that drives the antenna in any radio transmitter.

#### 1.1 Motivation

If the objective is an inexpensive, portable, high-performance transceiver, the desirability of certain circuit characteristics is clear. A low-cost solution is likely to be one in which as many circuit blocks as possible are implemented on the same chip: the cost savings result from the simplified PC (printed circuit) board. An inexpensive IC (integrated circuit) process, such as CMOS, translates directly into a cost savings. Portability implies at least two things from a circuit standpoint: small size, which is another advantage of a highly integrated

solution, and a long battery lifetime. Long battery lifetimes motivate low-power circuit techniques, so we add low power dissipation to the growing list of design constraints. What is meant by "high-performance" depends on the context. For purposes of this book, high-performance implies the ability to communicate at the highest data rate possible for a given channel bandwidth. Achieving this goal directs the system designer to linear modulation techniques, and the circuit designer to a means of achieving high linearity in the transmitter.

A transceiver's performance according to the metrics of degree of integration, power consumption, and transmitter linearity is usually dominated by the performance of the power amplifier. At even modest output powers (a few hundred milliwatts) it is far and away the most power-hungry system block in a transceiver, and the large voltage swings at its output push it deep into nonlinear regions of operation. The devices in most IC processes impose a maximum usable DC power supply voltage. Further, high-Q impedance transformations, which cannot always be realized on-chip, are sometimes necessary to achieve high output power levels.

It follows that improvements in transmitter performance depend on the progress made with the power amplifier. That observation motivates the investigation described in this book.

#### **1.2** Organization

The arc of this text generally proceeds from the abstract to the applied, culminating with a description of a fabricated chip designed to tie together many of the concepts treated here. Chapter 2 deals with the theoretical problem of realizing amplification with a cascade of stages. One design option is to employ *local* feedback around each of the individual stages. This chapter details the surprising result that a wide range of specifications, including linearity, can be optimized through intelligent choice of the feedback gains. That an optimum exists is perhaps not a surprise, but that this optimum can be found quickly and unambiguously is new and of considerable interest. The key is a technique called geometric programming.

The importance of linearity in radio transmitters is treated briefly in Chapter 3, together with a description of the tradeoff between linearity and power efficiency in power amplifiers. This chapter is also an exploration of the various common methods of softening this tradeoff, which can be grouped under the general heading of "linearization techniques."

Chapter 4 describes a new approach for achieving and maintaining phase alignment in Cartesian feedback power amplifiers. The focus here is on the theoretical principles of the new method, which during the investigation were validated by simulation and by a discrete-component prototype. A new technique for realizing accurate analog multiplication is developed as a means of improving the performance of the first prototype. A full analysis of this multiplication technique is presented here.

This book concludes with Chapter 5, a description of the culminating IC prototype, and Chapter 6, final thoughts. Readers interested in further details of the hardware prototypes are directed to the appendices.

This page intentionally left blank

#### Chapter 2

### OPTIMAL ALLOCATION OF LOCAL FEEDBACK IN MULTISTAGE AMPLIFIERS

The use of linear feedback around an amplifier stage was pioneered by Black [1], Bode [2], and others. The relations among the choice of feedback gain and the (closed-loop) gain, bandwidth, rise-time, sensitivity, noise, and distortion properties, are well understood (see, *e.g.*, [3]). For a single stage amplifier, the choice of the (single) feedback gain is a simple problem.

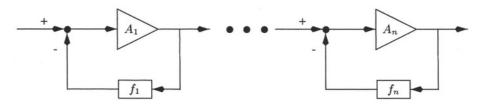

In this chapter we consider the *multistage* amplifier shown in figure 2.1, consisting of n open-loop amplifier stages denoted  $A_1, \ldots, A_n$ , with local feedback gains  $f_1, \ldots, f_n$  employed around the stages.<sup>1</sup>

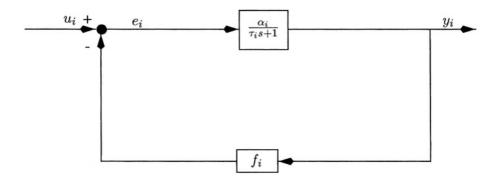

Figure 2.1. Block diagram of multistage amplifier.

We assume that the amplifier stages are fixed, and consider the problem of choosing the feedback gains  $f_1, \ldots, f_n$ . The choice of these feedback gains affects a wide variety of performance measures for the overall amplifier, including gain, bandwidth, rise-time, delay, noise, distortion and sensitivity properties, maximum output swing, and dynamic range. These performance measures depend on the feedback gains in a complicated and nonlinear manner. It is thus

<sup>&</sup>lt;sup>1</sup>Much of the material presented in this chapter originally appeared in the journal article [4], written by the author and coauthored by S. Boyd, M. Hershenson, and T. H. Lee.

far from clear, given a set of specifications, how to find an optimal choice of feedback gains. We refer to the problem of determining optimal values of the feedback gains, for a given set of specifications on overall amplifier performance, as the *local feedback allocation problem*.

We will show that the local feedback allocation problem can be cast as a *geometric program* (GP), which is a special type of optimization problem. Even complicated geometric programs can be solved very efficiently, and globally, by recently developed interior-point methods (see [5, 6,7]). Therefore we are able to give a complete, global, and efficient solution to the local feedback allocation problem.

In section 2.1, we give a detailed description of the models of an amplifier stage used to analyze the performance of the amplifier. Though simple, the models capture the basic qualitative behavior of a source-degenerated differential pair. In section 2.2, we derive expressions for the various performance measures for the overall amplifier, in terms of the local feedback gains. In section 2.3, we give a brief description of geometric programming, and in section 2.4, we put it all together to show how the optimal local feedback allocation problem can be cast as a geometric program, and design examples are given in section 2.5. A summary of the method follows in section 2.6, along with a treatment of a specific circuit example in section 2.7. This chapter closes with section 2.8, a discussion of the relevance of local feedback allocation to power amplifier linearization.

#### 2.1 Amplifier stage models

In this section we describe several different models of an amplifier stage, used for various types of analysis.

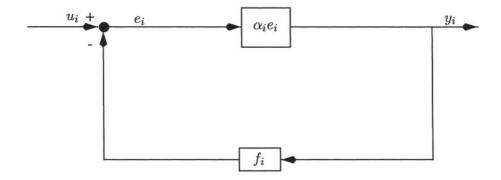

#### 2.1.1 Linearized static model

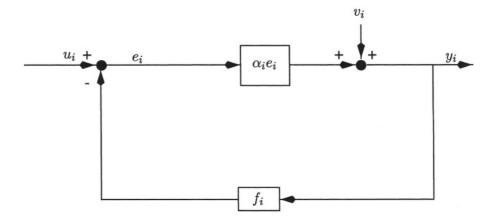

The simplest model we use is the linear static model shown in figure 2.2. The stage is characterized by  $y_i = \alpha_i e_i$ , where  $\alpha_i$  is the gain of the *i*th stage, which we assume to be positive. We will use this simple model for determining the overall gain of the amplifier, determining the maximum signal swing, and the sensitivity of the amplifier gain to each stage gain.

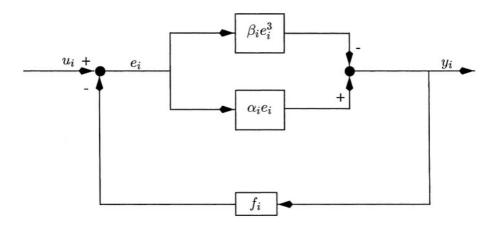

#### 2.1.2 Static nonlinear model

To quantify nonlinear distortion effects, we use a static nonlinear model of the amplifier stage as shown in figure 2.3. We assume that the nonlinearity or transfer characteristic has the form

$$y_i = a_i(e) = \alpha_i e - \beta_i e^3 + o(e^3),$$

(2.1)

Figure 2.2. Linearized static model of amplifier stage.

Figure 2.3. Nonlinear static model of amplifier stage.

where  $o(e^3)$ , which indicates terms of order higher than three, is assumed to be negligible. This form is inspired by the transfer characteristic of a sourcecoupled pair [8], and is a general model for third-order nonlinearity in a stage with an odd transfer characteristic. The function  $a_i(\cdot)$  is the *transfer characteristic* of the *i*th stage, and  $\beta_i$  is the *third-order coefficient* of the amplifier stage. Note that the gain and third-order coefficient are related to the transfer characteristic by

$$\alpha_i = a'_i(0), \quad \beta_i = -\frac{a'''_i(0)}{6}.$$

(2.2)

We assume that  $\beta_i \ge 0$ , which means the third-order term is *compressive*: as the signal level increases from zero, the nonlinear term tends to decrease the output amplitude when compared to the linear model.

#### 2.1.3 Linearized dynamic model

To characterize the bandwidth, delay, and rise-time of the overall amplifier, we use the linearized dynamic model shown in figure 2.4. Here the stage is represented by a simple one-pole transfer function with time constant  $\tau_i$  (which we assume to be positive).

Figure 2.4. Linear dynamic model of amplifier stage.

#### 2.1.4 Static noise model

Last, we have the static noise model shown in figure 2.5, which includes a simple output-referred noise  $v_i$ . As will become clear later, more complicated noise models including input noise, or noise injected in the feedback loop, are also readily handled by this method. Our noise model is characterized by the rms value of the noise source, which we denote  $\overline{v_i}$ . We assume that noise sources associated with different stages are uncorrelated.

#### 2.2 Amplifier analysis

In this section we derive expressions for various performance indices for the overall amplifier. For analytical convenience, we express these indices in terms of the *return differences:*

$$l_i = 1 + f_i \alpha_i. \tag{2.3}$$

In the analysis that follows, it is assumed that the dynamic interaction between amplifier stages can be formulated as shown in section 2.7.3.

Figure 2.5. Static noise model of amplifier stage.

#### 2.2.1 Gain and output swing

We consider the linear static model of section 2.1.1. The gain of the amplifier, from input  $u_1$  to the output of the *k*th stage  $y_k$ , is given by

$$\prod_{i=1}^{k} \frac{\alpha_i}{1 + \alpha_i f_i} = \prod_{i=1}^{k} \frac{\alpha_i}{l_i},$$

(2.4)

and the overall gain, from  $u_1$  to  $y_n$ , is given by

$$\tilde{\alpha} = \prod_{i=1}^{n} \frac{\alpha_i}{l_i}.$$

(2.5)

Here, of course,  $\alpha_i/l_i$  is the familiar expression for the closed-loop gain of the *i*th stage. It will be convenient later to use the notation

$$\tilde{\alpha}_i = \frac{\alpha_i}{l_i} \tag{2.6}$$

to denote the closed-loop gain of the *i*th stage. (In general, we will use the tilde to denote a closed-loop quantity.)

Now suppose the input signal level is  $U = |u_1|$ , and that the *i*th stage has a maximum allowed output signal level of  $Y_i$ , *i.e.*, we require  $|y_i| \le Y_i$ . This in turn means that for k = 1, ..., n, we have

$$U\prod_{i=1}^{k}\frac{\alpha_i}{l_i} \le Y_k,\tag{2.7}$$

so the maximum allowed input signal level is

$$U_{\max} = \max_{k=1,\dots,n} Y_k \prod_{i=1}^k \frac{l_i}{\alpha_i}.$$

(2.8)

The maximum allowed output signal level is found by multiplying by the overall gain:

$$Y_{\max} = \max_{k=1,\dots,n} Y_k \prod_{i=k+1}^n \frac{\alpha_i}{l_i}$$

(2.9)

(where the empty product, when i = n, is interpreted as one).

#### 2.2.2 Sensitivity

The (logarithmic) sensitivity of the overall amplifier gain to the open-loop gain of the *i*th stage is given by

$$S_i = \frac{\partial \log \tilde{\alpha}}{\partial \log \alpha_i} = \frac{1}{l_i}.$$

(2.10)

#### 2.2.3 Nonlinearity

We begin by deriving the closed-loop third-order coefficient of a single feedback amplifier stage, using the static nonlinear model of section 2.1.2. The output y is related to the input u through the relation

$$y = a(u - fy).$$

(2.11)

Differentiating both sides with respect to u leads to the familiar result from elementary feedback theory:

$$y'(0) = \frac{a'(0)}{1 + fa'(0)} = \frac{\alpha}{l} = \tilde{\alpha}.$$

(2.12)

Differentiating again yields

$$y''(0) = \frac{a''(0)}{l^3} = 0,$$

(2.13)

and, once more,

$$y'''(0) = \frac{a'''(0)l - 3fa''(0)^2}{l^5} = -\frac{6\beta}{l^4},$$

(2.14)

using  $a'''(0) = -6\beta$  and a''(0) = 0 from the previous equation. This equation shows that the third-order coefficient of the closed-loop transfer characteristic is given by

$$\tilde{\beta} = \frac{y'''(0)}{6} = \frac{\beta}{l^4}.$$

(2.15)

This is the well-known result showing the linearizing effect of (linear) feedback on an amplifier stage.

Next, consider a cascade of two amplifier stages. Let the transfer characteristics of two stages be  $y_1(\cdot)$  and  $y_2(\cdot)$ . We write

$$\phi_2(u) = y_2(y_1(u)) \tag{2.16}$$

and differentiate:

$$\begin{aligned}

\phi_2'(0) &= y_2'(0)y_1'(0), \\

\phi_2''(0) &= y_2'(0)y_1''(0) + (y_1'(0))^2 y_2''(0),

\end{aligned}$$

(2.17)

and so

$$\phi_{2}^{\prime\prime\prime}(0) = y_{2}^{\prime}(0)y_{1}^{\prime\prime\prime}(0) + y_{1}^{\prime}(0)^{3}y_{2}^{\prime\prime\prime}(0) +3y_{2}^{\prime\prime}(0)y_{1}^{\prime\prime}(0)y_{1}^{\prime\prime}(0).$$

(2.18)

Since  $y_1$  and  $y_2$  are both odd functions, the last term vanishes. Therefore the third-order coefficient of the cascade of the two stages is given by

$$\tilde{\beta}_1 \tilde{\alpha}_2 + \tilde{\beta}_2 \tilde{\alpha}_1^3. \tag{2.19}$$

More generally, the third-order coefficient of a cascade of n stages can be expressed as

$$\tilde{\beta} = \sum_{i=1}^{n} \left[ \left( \prod_{k=1}^{i-1} \tilde{\alpha}_k^3 \right) \tilde{\beta}_i \left( \prod_{j=i+1}^{n} \tilde{\alpha}_j \right) \right].$$

(2.20)

This very complicated formula gives the relation between the local return differences and the third-order coefficient of the overall amplifier.

#### 2.2.4 Bandwidth

We next examine the linearized dynamic performance of the amplifier chain, using the stage model given in section 2.1.3. The transfer function of an individual stage is given by

$$\frac{Y_i(s)}{U_i(s)} = \frac{\alpha_i/(\tau_i s+1)}{1+f_i \alpha_i/(\tau_i s+1)} = \frac{\tilde{\alpha}_i}{\tilde{\tau}_i s+1},$$

(2.21)

where  $\tilde{\tau}_i = \tau_i / l_i$  is the closed-loop time constant of the *i*th stage. The transfer function of the entire cascade amplifier immediately follows:

$$H(s) = \prod_{i=1}^{n} \frac{\tilde{\alpha}_i}{\tilde{\tau}_i s + 1}.$$

(2.22)

The -3dB bandwidth of the amplifier is defined as the smallest frequency  $\omega$  for which  $|H(j\omega)| = |H(0)|/\sqrt{2}$ .

#### 2.2.5 Delay and rise-time

The rise-time and delay of the overall amplifier can be characterized in terms of the moments of the impulse response, as described in [9]. The delay is the normalized first moment of the impulse response of the system:

$$t_{\rm d} = \frac{\int_{-\infty}^{\infty} th(t)dt}{\int_{-\infty}^{\infty} h(t)dt}.$$

(2.23)

Using basic properties of the Laplace transform and results from section 2.2.4, we have

$$t_{\rm d} = \frac{-\frac{dH(s)}{ds}\Big|_{s=0}}{H(0)} = -\frac{d}{ds} \prod_{i=1}^{n} \frac{1}{\tilde{\tau}_i s + 1} \Big|_{s=0} = \sum_{i=1}^{n} \tilde{\tau}_i = \sum_{i=1}^{n} \frac{\tau_i}{l_i}.$$

(2.24)

This formula shows the exact relation between the overall amplifier delay (as characterized by the first moment of the impulse response) and the local return differences  $l_i$ .

We use the second moment of the impulse response,

$$t_{\rm r}^2 = 4 \left[ \frac{\int_{-\infty}^{\infty} t^2 h(t) dt}{\int_{-\infty}^{\infty} h(t) dt} - t_{\rm d}^2 \right],$$

(2.25)

as a measure of the square of the rise-time of the overall amplifier in response to a step input. Again making use of Laplace transform identities, we express (2.25) in terms of the transfer function H(s):

$$t_{\rm r}^2 = \frac{4}{H(0)} \left[ \left. \frac{d^2}{ds^2} H(s) \right|_{s=0} - t_{\rm d}^2 \right].$$

(2.26)

Substituting the transfer function of the amplifier, given in equation (2.22), we find that the rise-time of the overall amplifier is

$$t_{\rm r}^2 = 4 \sum_{i=1}^n \frac{\tau_i^2}{l_i^2}$$

(2.27)

(using the fact that the closed-loop rise-time of the *i*th stage is  $2\tilde{\tau}_i$ ).

#### 2.2.6 Noise and dynamic range

We now consider the static noise model of section 2.1.4. The mean-squared noise amplitude at the output of the overall amplifier can be written

$$\overline{v_{\text{out}}^2} = \sum_{i=1}^n \left( \frac{\overline{v_i}^2}{l_i^2} \left[ \prod_{j=i+1}^n \frac{\alpha_j}{l_j} \right]^2 \right).$$

(2.28)

The input-referred mean-squared noise is then

$$\overline{v_{\text{in}}^2} = \frac{\overline{v_{\text{out}}^2}}{\tilde{\alpha}^2} = \sum_{i=1}^n \left( \frac{\overline{v_i^2}}{\alpha_i^2} \left[ \prod_{j=1}^{i-1} \frac{l_j}{\alpha_j} \right]^2 \right).$$

(2.29)

The *dynamic range* of the amplifier is the ratio of maximum output voltage to output-referred RMS noise level, expressed in decibels:

$$DR = 20 \log_{10} \frac{Y_{\text{max}}}{\overline{v_{\text{out}}}}.$$

(2.30)

#### 2.2.7 SFDR and IIP linearity measures

We conclude this analysis by obtaining expressions for the spurious-free dynamic range (SFDR) and the input-referred third-order intercept point (IIP3). They are both readily derived from the results in 2.2.3 through 2.2.6, and so contain no new information or analysis, but they are widely used performance indices for the amplifier.

SFDR and IIP3 give information about the linearity of an amplifier. They concern the results of the following experiment: inject a signal  $v \cos \omega_1 t + v \cos \omega_2 t$  at the input, and examine the output for the presence of intermodulation (IM) products. We concern ourselves here with third-order IM products, which owe their existence to non-zero  $\beta_i$ . The third order intermodulation products are:

$$\begin{bmatrix} \frac{3}{4}\tilde{\beta}v^3 \end{bmatrix} [\cos(\omega_1 + 2\omega_2)t + \cos(\omega_1 - 2\omega_2)t + \cos(2\omega_1 + \omega_2)t + \cos(2\omega_1 - \omega_2)t].$$

(2.31)

The SFDR is defined as the signal-to-noise ratio when the power in each third order intermodulation product equals the noise power at the output [10]. To derive the SFDR, we simply refer a third order IM product back to the input and equate its amplitude to the input-referred RMS noise amplitude:

$$\frac{1}{\tilde{\alpha}} \left[ \frac{3}{4} \tilde{\beta} v^3 \right] = \overline{v_{\rm in}}.$$

(2.32)

The SFDR in decibels is then given by

$$SFDR = \frac{2}{3}(10) \log_{10} \left( \frac{\frac{4}{3} \left| \frac{\alpha}{\beta} \right|}{\overline{v_{in}^2}} \right).$$

(2.33)

The IIP3 is the input power at which the amplitude of the third-order IM products equals the input. Mathematically, we require

$$\left|\tilde{\alpha}v\right| = \left|\frac{4}{3}\tilde{\beta}v^3\right|.$$

(2.34)

Normalizing the input resistance to unity for convenience, we have for IIP3

$$IIP3 = \frac{2}{3} \left| \frac{\tilde{\alpha}}{\tilde{\beta}} \right|.$$

(2.35)

#### 2.3 Geometric programming

Let f be a real-valued function of n real, positive variables  $x_1, x_2, \ldots, x_n$ . It is called a *posynomial* function if it has the form

$$f(x_1, \dots, x_n) = \sum_{k=1}^{t} c_k x_1^{\alpha_{1k}} x_2^{\alpha_{2k}} \cdots x_n^{\alpha_{nk}}$$

(2.36)

where  $c_j \ge 0$  and  $\alpha_{ij} \in \mathbf{R}$ . When t = 1, f is called a *monomial* function. Thus, for example,  $0.7 + 2x_1/x_3^2 + x_2^{0.3}$  is posynomial and  $2.3(x_1/x_2)^{1.5}$  is a monomial. Posynomials are closed under sums, products, and nonnegative scaling.

A geometric program (GP) has the form

minimize

$$f_0(x)$$

subject to  $f_i(x) \le 1$ ,  $i = 1, 2, ..., m$ ,

$g_i(x) = 1$ ,  $i = 1, 2, ..., p$ ,

$x_i > 0$ ,  $i = 1, 2, ..., n$ ,

(2.37)

where  $f_i$  are posynomial functions and  $g_i$  are monomial functions. Geometric programs were introduced by Duffin, Peterson, and Zener in the 1960s [11].

The most important property of geometric programs for us is that they can be solved, with great efficiency, and globally, using recently developed interiorpoint methods [7, 5]. Geometric programming has recently been used to optimally design electronic circuits including CMOS op-amps [12, 13] and planar spiral inductors [14].

Several simple extensions are readily handled by geometric programming. If f is a posynomial and g is a monomial, then the constraint  $f(x) \leq g(x)$  can be expressed as  $f(x)/g(x) \leq 1$  (since f/g is posynomial). In particular, constraints of the form  $f(x) \leq a$ , where a > 0 is a constant, can also be used. Similarly, if  $g_1$  and  $g_2$  are both monomial functions, the constraint  $g_1(x) = g_2(x)$  can be expressed as  $g_1(x)/g_2(x) = 1$  (since  $g_1/g_2$  is monomial). If g is a monomial, we can maximize it by minimizing the posynomial function 1/g.

#### 2.3.1 Geometric programming in convex form

A geometric program can be reformulated as a *convex optimization problem*, *i.e.*, the problem of minimizing a convex function subject to convex inequalities constraints and linear equality constraints. This is the key to our ability to globally and efficiently solve geometric programs. We define new variables

$y_i = \log x_i$ , and take the logarithm of a posynomial f to get

$$h(y) = \log \left( f\left(e^{y_1}, \dots, e^{y_n}\right) \right) = \log \left(\sum_k^t e^{a_k^T y + b_k}\right)$$

(2.38)

where  $a_k^T = [\alpha_{1k} \cdots \alpha_{nk}]$  and  $b_k = \log c_k$ . It can be shown that *h* is a *convex* function of the new variable *y*: for all  $y, z \in \mathbf{R}^n$  and  $0 \le \lambda \le 1$  we have

$$h(\lambda y + (1 - \lambda)z) \le \lambda h(y) + (1 - \lambda)h(z).$$

(2.39)

Note that if the posynomial f is a monomial, then the transformed function h is affine, *i.e.*, a linear function plus a constant.

We can convert the standard geometric program (2.37) into a convex program by expressing it as

#### minimize $\log f_0(e^{y_1}, \dots, e^{y_n})$ subject to $\log f_i(e^{y_1}, \dots, e^{y_n}) \le 0, \quad i = 1, \dots, m$ $\log g_i(e^{y_1}, \dots, e^{y_n}) = 0, \quad i = 1, \dots, p.$ (2.40)

This is the so-called *convex form* of the geometric program (2.37). Convex programs have several important characteristics. Chief among these is that convex programs are solvable using efficient interior-point methods. Additionally, there is a complete and useful duality, or sensitivity, theory for convex programs [5].

#### 2.3.2 Solving geometric programs

Since Ecker's survey paper [6] there have been several important developments related to solving geometric programs in the exponential form. A huge improvement in computational efficiency was achieved in 1994, when Nesterov and Nemirovsky developed efficient interior-point algorithms to solve a variety of nonlinear optimization problems, including geometric programs [7]. Recently, Kortanek et al. have shown how the most sophisticated primal-dual interior-point methods used in linear programming can be extended to geometric programming, resulting in an algorithm approaching the efficiency of current interior-point linear programming solvers [15]. The algorithm they describe has the desirable feature of exploiting sparsity in the problem, *i.e.*, efficiently handling problems in which each variable appears in only a few constraints.

For our purposes, the most important feature of geometric programs is that they can be *globally* solved with great efficiency. Problems with hundreds of variables and thousands of constraints are readily handled, on a small workstation, in minutes. The problems we encounter in this chapter, which have a few tens of variables and fewer than 100 constraints, are easily solved in under one second. Perhaps even more important than the great efficiency is the fact that algorithms for geometric programming always obtain the global minimum. Infeasibility is unambiguously detected: if the problem is infeasible, then the algorithm will determine this fact, and not just fail to find a feasible point. Another benefit of the global solution is that the initial starting point is irrelevant. We emphasize that the same global solution is found no matter what the initial starting point is.

These properties should be compared to general methods for nonlinear optimization, such as sequential quadratic programming, which only find *locally* optimal solutions, and cannot unambiguously determine infeasibility. As a result, the starting point for the optimization algorithm does have an affect on the final point found. Indeed, the simplest way to lower the risk of finding a local, instead of global, optimal solution, is to run the algorithm several times from different starting points. This heuristic only reduces the risk of finding a nonglobal solution. For geometric programming, in contrast, the risk is always exactly zero, since the global solution is always found regardless of the starting point.

#### 2.4 Optimal local feedback allocation

We now make the following observation, based on the results of section 2.2: a wide variety of specifications for the performance indices of the overall amplifier can be expressed in a form compatible with geometric programming using the variables  $l_i$ . The startling implication is that optimal feedback allocation can be determined using geometric programming.

The true optimization variables are the feedback gains  $f_i$ , but we will use instead the return differences  $l_i$ , with the constraints  $l_i \ge 1$  imposed to ensure that  $f_i \ge 0$ . Once we determine the optimal values for  $l_i$ , we can find the optimal feedback gains via

$$f_i = (l_i - 1)/\alpha_i.$$

(2.41)

#### 2.4.1 Closed-loop gain

The closed-loop gain  $\tilde{\alpha}$  is given by the monomial expression (2.5). Therefore we can impose any type of constraint on the closed-loop gain. We can require it to equal a given value, for example, or specify a minimum or maximum value for the closed-loop gain. Each of these constraints can be handled by geometric programming.

#### 2.4.2 Maximum signal swing

The maximum output signal swing is given by the expression (2.9). The constraint that the output swing exceed a minimum required value, *i.e.*,  $Y_{\text{max}} \ge$

$\gamma$ , can be expressed as

$$Y_k \prod_{i=k+1}^n \frac{\alpha_i}{l_i} \ge \gamma, \quad k = 1, \dots, n.$$

(2.42)

Each of these inequalities is a monomial inequality, and hence can be handled by geometric programming. Note that we also allow the bound on signal swing, *i.e.*,  $\gamma$ , as a variable here.

#### 2.4.3 Sensitivity

The sensitivity of the amplifier to the *i*th stage gain is given by the monomial expression (2.10). It follows that we can place an upper bound on the sensitivity (or, if we choose, a lower bound or equality constraint).

#### 2.4.4 Bandwidth

Consider the constraint that the closed-loop -3dB bandwidth should exceed  $\Omega$ . Since the magnitude of the transfer function of the amplifier is monotonically decreasing as a function of frequency, this is equivalent to imposing the constraint

$$|H(j\Omega)| \ge \frac{1}{\sqrt{2}}H(0), \qquad (2.43)$$

which we can rewrite as

$$\frac{1}{|H(j\Omega)|^2} \le \frac{2}{H(0)^2}.$$

(2.44)

Now using the expression for the transfer function,

$$H(j\omega) = \prod_{i=1}^{n} \frac{\alpha_i}{j\tau_i\omega + l_i},$$

(2.45)

we can write the bandwidth constraint as

$$\left|\frac{1}{H(j\Omega)}\right|^2 = \prod_{i=1}^n \frac{(\tau_i \Omega)^2 + l_i^2}{\alpha_i^2} \le 2 \prod_{i=1}^n \frac{l_i^2}{\alpha_i^2}.$$

(2.46)

This, in turn, we can express as

$$\prod_{i=1}^{n} \frac{(\tau_i \Omega)^2 + l_i^2}{l_i^2} \le 2.$$

(2.47)

This is a complicated, but posynomial, inequality in the variables  $l_i$ , hence it can be handled by geometric programming. Note that we can even make the minimum -3dB bandwidth  $\Omega$  a variable, and maximize it.

# 2.4.5 Noise and dynamic range

The expression (2.29) for the input-referred noise power, is a posynomial functions of the variables  $l_1, \ldots, l_n$ . Therefore we can impose a maximum on the input-referred noise level, using geometric programming.

The requirement that the dynamic range exceed some minimum allowed value  $DR_{min}$ , *i.e.*,  $DR \ge DR_{min}$ , can be expressed as

$$\frac{\overline{v_{\text{out}}^2}}{\gamma} \le 10^{-\text{DR}/10},$$

(2.48)

where  $\gamma$  is the bound on signal swing defined in (2.42). Therefore, this constraint can be handled by geometric programming.

# 2.4.6 Delay and rise-time

As can be seen in equations (2.24) and (2.27), the expressions for delay and rise-time are posynomial functions of the return differences  $l_i$ . A maximum on each can thus be imposed.

#### 2.4.7 Third-order distortion

The expression for third-order coefficient, given in (2.20), is a posynomial, so we can impose a maximum on the third-order coefficient.

## 2.4.8 SFDR and IIP3

Consider the constraint that the SFDR should exceed some minimum value  $\gamma$ . Using the expression (2.33), we can write this as

$$\frac{2}{3}(10)\log_{10}\left(\frac{\frac{4}{3}|\tilde{\frac{\alpha}{\beta}}|}{\overline{v_{\rm in}}^2}\right) \ge \gamma.$$

(2.49)

This can be written as

$$\frac{4}{3}\frac{\tilde{\alpha}}{\tilde{\beta}}\frac{1}{\frac{1}{v_{\rm in}^2}} \ge 10^{3\gamma/20}.$$

(2.50)

This can be handled by geometric programming by writing it as

$$\frac{\tilde{\beta}}{\tilde{\alpha}}\overline{v_{\rm in}^2} \le \frac{3}{4}10^{-3\gamma/20}.\tag{2.51}$$

## 2.5 Design Examples

The foregoing analysis shows that complicated problems of feedback allocation can be expressed as globally solved geometric programs. We can take as an objective any of the posynomial performance measures described above, and apply any combination of the constraints described above. We can also compute optimal trade-off curves by varying one of the specifications or constraints over a range, computing the optimal value of the objective for each value of the specification.

We provide in this section a few system-level examples. In the section 2.7, we demonstrate a circuit-level application using the common source-coupled pair.

# 2.5.1 Trade-offs among bandwidth, gain, and noise

In our first example we consider a three-stage amplifier, with all stages identical, with parameters

$$\alpha_i = 10, \qquad \tau_i = 10^{-6} \text{sec}, \qquad \overline{v_{n,i}} = 4.07 \mu \text{V}.$$

(2.52)

The required closed-loop gain is 23.5dB. We maximize the bandwidth, subject to the equality constraint on closed-loop gain, and a maximum allowed value of input-referred noise.

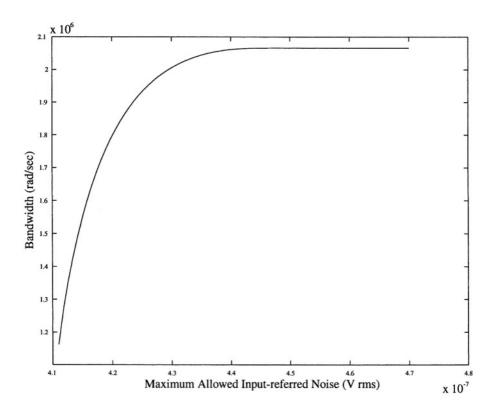

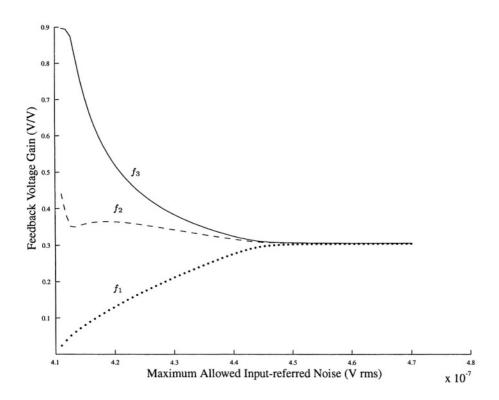

Figure 2.6 shows the optimal bandwidth achieved, as a function of the maximum allowed input-referred noise. As it must, the optimal bandwidth increases as we relax (increase) the input-referred noise limit. Figure 2.7 shows the optimal values of the feedback gains as the input-referred noise limit varies.

These curves roughly identify two regions in the design space. In one, the noise constraint is so relaxed as to not be an issue. The program identifies the optimum bandwidth solution for the given gain, which is to place all of the closed loop poles in the same place. In the other, the tradeoff between bandwidth and noise is strong. Equation (2.29) shows that the noise contribution of  $\overline{v_{n,1}}$  is independent of  $l_1$ , but the noise contributions of the following stages can be diminished by making  $l_1$  (and therefore  $f_1$ ) small. It follows that  $f_3$  is the greatest of the feedback gains, followed by  $f_2$  and  $f_1$ .

We can also examine the optimal trade-off between bandwidth and required DC gain. Here we impose the fixed limit on input-referred noise at  $4.15 \times 10^{-7}$  V rms, and maximize the bandwidth subject to a required closed-loop gain.

Figures 2.8 and 2.9 show the maximum attainable bandwidth and the optimal feedback gain allocation as a function of the required closed-loop gain. Again we see two regions in design space caused by the noise constraint.

Figure 2.6. Maximum bandwidth versus limit on input-referred noise.

*Figure 2.7.* Optimal feedback allocation pattern, for maximum bandwidth with limit on inputreferred noise. Gain = 23.5dB.

*Figure 2.8.* Maximum bandwidth versus required closed-loop gain. Maximum input-referred noise = 4.15e-7 V rms.

*Figure 2.9.* Optimal feedback allocation pattern for maximum bandwidth versus required closed-loop gain. Maximum input-referred noise = 4.15e-7 V rms.

#### 2.5.2 SFDR versus gain

In this example, we again consider a three-stage amplifier, now with identical stages having parameters

$$\alpha_i = 10, \qquad \beta_i = 0.667 \mathrm{V}^{-2}, \qquad \overline{v_{n,i}} = 4.07 \mu \mathrm{V}.$$

(2.53)

We maximize the spurious-free dynamic range subject to an equality constraint on the overall gain. Figure 2.10 shows the achieved SFDR as a function of the required gain, and figure 2.11 shows the associated optimal gain allocation patterns.

Figure 2.10. Maximum spurious-free dynamic range versus required gain.

In addition to obtaining optimal designs from the figures 2.10 and 2.11, we observe a qualitative trend: feedback gain is allocated preferentially to stages furthest down the signal chain. This is in agreement with sound engineering judgment, and with the results of section 2.5.1.

We can also argue from the standpoint of optimum linearity that figure 2.11 makes sense. Nonlinearity in the later stages, where the signal amplitude is the

Figure 2.11. Optimal feedback allocation pattern for maximum spurious-free dynamic range versus required gain.

largest, will cause the most severe harmonic distortion. It follows that feedback should be applied more aggressively in later stages.

## 2.5.3 Stage selection

The method described in chapter computes the globally optimal values of the local feedback gains, with the amplifier models fixed. We can use the method indirectly to optimally choose each stage, from a set of possible choices, in addition to optimally allocating feedback around the stages. Suppose we have a set of m possible choices for each of n stages. By computing the optimal performance for each  $m^n$  possible combinations of stages, we can then determine the optimal combination as well as the optimal feedback gains. Of course the effort required to exhaustively search over the combinations grows rapidly with the number of stages, but is certainly feasible for moderate numbers of stages, *e.g.*, fewer than six or so.

We demonstrate this method for optimal stage selection with an example. Table 2.1 shows a listing of three candidate stages for use in a multistage amplifier design. Amplifier A can be seen to have the best linearity and the worst

| Amplifier Designation | $\alpha_i$ | $\beta_i$ | $\overline{v_n}$ |

|-----------------------|------------|-----------|------------------|

| A                     | 10         | 0.67      | $41\mu V$        |

| В                     | 10         | 6.7       | $4.1\mu V$       |

| С                     | 10         | 67        | $0.41 \mu V$     |

| Table | 2.1. | Candidate | stages. |

|-------|------|-----------|---------|

|-------|------|-----------|---------|

noise, amplifier C has the worst linearity and the best noise, and amplifier B is in between.

Our goal is to maximize SFDR, subject to a required gain of 46dB, for a three-stage design. By solving all 27 combinations, we find that the optimal combination of stages and feedback is

**Stage 1** amplifier C, with f = 0.00023,

Stage 2 amplifier B, with f = 0.06589,

Stage 3 amplifier A, with f = 0.20072,

which achieves the optimal SFDR of 85dB.

This solution makes sense. The low-noise stage is used for the first stage (which is more critical for noise, since its noise is amplified by subsequent stages), and the high-linearity stage is used for the last stage (which handles larger signals, and so is more critical for distortion). Note that in this particular case, the optimal solution is to operate the first two stages essentially open-loop.

# 2.6 Geometric programming summary

In this chapter we show how to globally and efficiently solve the problem of optimally allocating local feedback gains in a multistage amplifier by posing the problem in the form of a geometric program. This formulation can handle a wide variety of practical objectives and constraints, and allows us to rapidly compute globally optimal trade-off curves among competing specifications.

We mention several extensions that are readily handled. While perhaps involved, it is not hard to work out the corresponding (posynomial) formulas for distortion characteristics that have fourth, fifth, or even higher order terms. It is also easy to handle a more sophisticated noise model, in which the noise is injected at several locations in the feedback around each stage, and notjust at the output as in the current model. In each case, the resulting noise power expression is still posynomial, and therefore can be handled by geometric programming. Another extension is to couple the design of the feedback together with the actual component-level design of the amplifier (for example, transistor widths and lengths), as in [16].

We envision several situations where the methods described in this chapter would be very useful to a circuit designer. Whenever the number of stages is at least three, and the number of important specifications is at least three (say), the problem of optimally allocating local feedback gains becomes quite complex, and a tool that completely automates this process is quite useful. When the number of stages reaches five or six, and the absolute optimal performance is sought, our method will far outperform even a good designer adjusting gains in an ad hoc manner.

# 2.7 An example application

The foregoing analysis establishes feedback allocation as a solvable problem. The extension of our technique to real world applications, however, begs clarification: we (seemingly) ignore loading between stages, choose suspiciously simple single-pole dynamics, etc.. We thus include the following example, in which we consider the ubiquitous source-coupled pair as our basic open-loop stage. Local feedback is allocated in the form of source degeneration, and all other characteristics (bias currents, load resistances, transistor sizes, etc.) are fixed.<sup>2</sup>

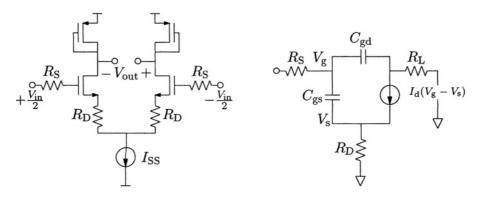

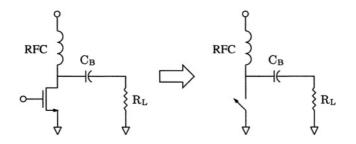

Figure 2.12 shows the basic stage that we consider. The differential half-

Figure 2.12. CMOS source-coupled pair and differential half-circuit.

circuit on the right should not be taken to represent the traditional "small-signal" model, as the dependent current source models a MOSFET operating in the saturation regime. The capacitors  $C_{gg}$  and  $C_{gd}$  are linear capacitors [10], and the

<sup>&</sup>lt;sup>2</sup>These, too, can be optimized via geometric programming. See, for example, [13], [12].

PMOS devices provide the resistances  $R_{\rm L}$ . We show in the following paragraphs how this common structure maps to the theoretical framework outlined in section 2.1.

#### 2.7.1 Linearized static model

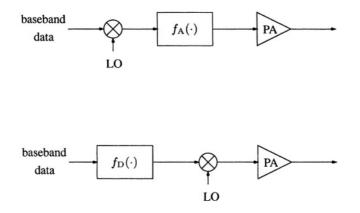

For this model the capacitors shown in figure 2.12 become open circuits, and the mapping from figure 2.2 to figure 2.13 is straightforward. A few short lines

Figure 2.13. Source degeneration as a form of feedback.

of algebra lead to the familiar gain expression:

$$A_{\rm v} = \left(\frac{g_{\rm m}}{1 + g_{\rm m} R_{\rm D}}\right) R_{\rm L}.$$

(2.54)

Already, it can be seen that  $l_i$  from the foregoing analysis finds its place here as  $(1 + g_m R_D)_i$ , with  $R_D$  taking the place of feedback gain. We emphasize that this is not merely a mathematical accident, but points to the physically meaningful interpretation of degeneration as a feedback mechanism.

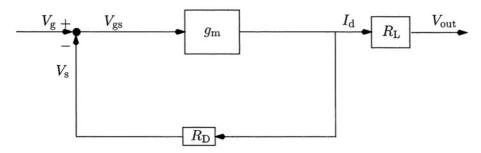

# 2.7.2 Static nonlinear model

Here, we modify figure 2.13 by replacing  $g_{\rm m}$  with  $G_{\rm m}(\cdot)$ , the nonlinear expression for drain current as a function of  $V_{\rm gs}$ . The expression for differential output current  $I_{\rm d}$  as a function of differential gate voltage  $V_{\rm g}$  for a general source-coupled pair is given in Gray and Meyer [8]. We reproduce it here:

$$I_{\rm d} = \mu_{\rm n} \frac{C_{\rm ox} W}{2L} V_{\rm g} \sqrt{\left(\frac{2I_{\rm SS}}{\mu_{\rm n} \left(\frac{C_{\rm ox} W}{2L}\right)}\right) - (V_{\rm g})^2}.$$

(2.55)

All constants in this formula are MOSFET parameters, and  $I_{SS}$  is the value of the current source in figure 2.12. For our purposes, a Taylor expansion of the square root allows us to write  $G_m(\cdot)$  as

$$G_{\rm m}(V_{\rm gs}) = \alpha V_{\rm gs} - \beta V_{\rm gs}^3 + \gamma V_{\rm gs}^5 - \cdots$$

(2.56)

Figure 2.14. Modification for nonlinear static model.

This is consistent with figure 2.3.

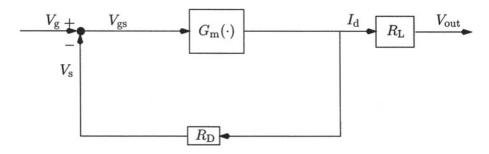

# 2.7.3 Linearized dynamic model

We use the Miller approximation described in Gray and Meyer [8], modified here to account for source degeneration. The Miller approximation (see fig-

Figure 2.15. Modeling dynamics using the Miller approximation.

ure 2.15) is the recognition that the dynamics of a single stage are dominated by a single pole, which arises from the interaction between source resistance  $R_s$  and the input capacitance. With no source degeneration, this input capacitance would be the sum of  $C_{gs}$  and the Miller multiplied  $C_{gd}$ :

$$C_{\rm T} = C_{\rm gs} + (1 + g_{\rm m} R_{\rm L}) C_{\rm gd} \simeq C_{\rm gs} + (g_{\rm m} R_{\rm L}) C_{\rm gd},$$

(2.57)

where have made the approximation that the gain,  $A_v = g_m R_L$ , is significantly greater than unity. This capacitance, together with the source resistance, creates

a pole with time constant  $\tau$ :

$$\tau = R_{\rm S}(C_{\rm gs} + (g_{\rm m}R_{\rm L})C_{\rm gd}).$$

(2.58)

Source degeneration causes the real part of the impedance looking into the gate to increase. At frequencies below the transistor's  $f_{\rm T}$ , however, the capacitive part still dominates and we replace  $C_{\rm gs}$  in the Miller formulation with

$$\frac{C_{\rm gs}}{1+g_{\rm m}R_{\rm D}}.$$

(2.59)

Source degeneration reduces the gain of the stage from  $g_{\rm m}R_{\rm L}$  to

$$\tilde{A}_{\rm v} = \frac{g_{\rm m} R_{\rm L}}{1 + g_{\rm m} R_{\rm D}}.$$

(2.60)

Our  $C_{\rm T}$  capacitance is accordingly modified to

$$\tilde{C}_{\rm T} \simeq \frac{C_{\rm gs}}{1 + g_{\rm m} R_{\rm D}} + \left(\frac{g_{\rm m} R_{\rm L}}{1 + g_{\rm m} R_{\rm D}}\right) C_{\rm gd}.$$

(2.61)

(We continue to assume that  $\tilde{A}_v$  is much greater than unity.) Finally, it can be seen that the effect of feedback has been to reduce the time constant of the pole by a factor of the return difference  $1 + g_m R_D$ , exactly as was shown in section 2.2.4:

$$\tilde{\tau} = R_{\rm S} \tilde{C}_{\rm T} = \frac{\tau}{1 + g_{\rm m} R_{\rm D}}.$$

(2.62)

If we define  $\tau$  as in equation 2.58, it can be seen that the source-coupled pair maps perfectly to figure 2.4.

Finally, note that the dynamics here, which are the poles formed by the output impedance of stage i with the input capacitance of stage i + 1, *are* the interstage loading effects.

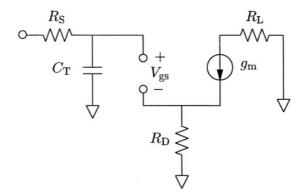

#### 2.7.3.1 An alternative formulation: open-circuit time constants

For bandwidth optimization in pure circuit systems, it is often useful to use the method of open-circuit time constants. The method may be summarized as computing the resistance  $R_i$  seen across the terminals of capacitors  $C_i$  with all other capacitors considered open circuits. The frequency  $\omega = \frac{1}{\sum_i R_i C_i}$  has been shown to be a good estimate of the -3dB bandwidth for many common circuits. Moreover this estimate, when applicable, is usually conservative. We direct the interested reader to the excellent discussions in [8] and [10].

We present this method as an alternative. For a given stage, the open-circuit resistance for  $C_{\rm gd}$  can be shown to be

$$R_{\rm gd} = R_{\rm S} + R_{\rm L} + \frac{g_{\rm m}}{1 + g_{\rm m} R_{\rm D}} R_{\rm S} R_{\rm L}, \qquad (2.63)$$

a simple posynomial in the design variable  $l = 1 + g_m R_D$ . For  $C_{gs}$ , the result is

$$R_{\rm gs} = \frac{R_{\rm S} + R_{\rm D}}{1 + g_{\rm m} R_{\rm D}},$$

(2.64)

which we write as the posynomial in l

$$R_{\rm gs} = \frac{1}{g_{\rm m}} + \left(R_{\rm S} - \frac{1}{g_{\rm m}}\right)l^{-1}.$$

(2.65)

# 2.7.4 Static noise model

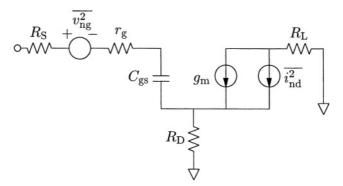

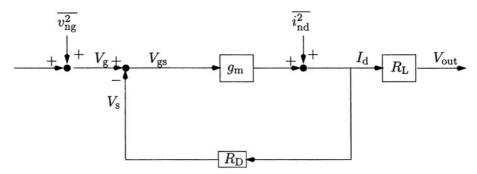

Two sources of noise in MOSFETs, drain noise and gate noise, share a common physical origin [10]. Figure 2.16 shows their places in the MOSFET model. Their corresponding places in our theoretical framework are clear, and

Figure 2.16. MOSFET noise model.

shown in figure 2.17. We only show the noise sources associated with the

Figure 2.17. MOSFET gate and drain noise.

active device itself. Resistors are known to introduce noise as well, and their contribution is straightforward to include. The noise of  $R_{\rm L}$ , for example, is naturally incorporated as part of the gate noise of the following stage. Similar manipulations can be done for  $R_{\rm D}$  and, of course,  $R_{\rm S}$ .

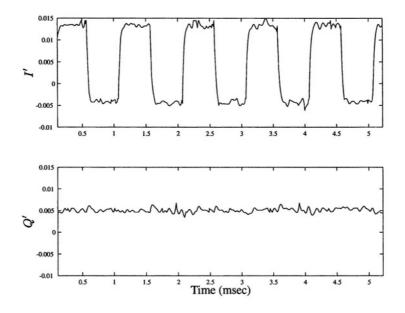

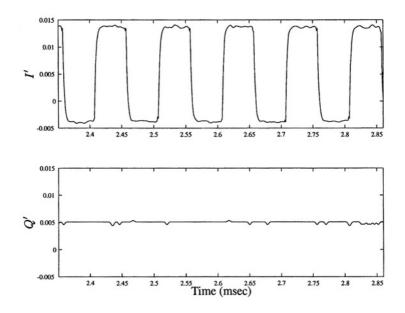

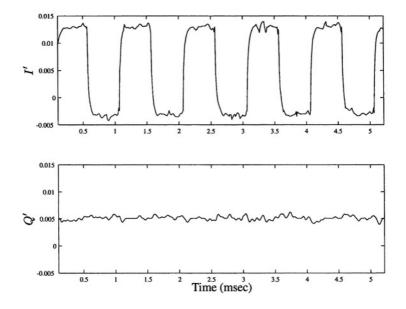

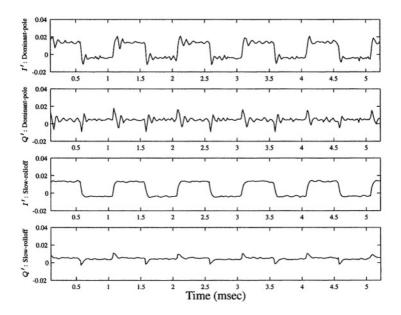

# **2.8** Local feedback allocation for power amplifier linearization